HD63484P98比較器的輸出狀態由D觸發器存儲

發布時間:2020/1/25 19:20:21 訪問次數:5477

hd63484p98別作為比較器c1~c7的參考電壓。輸入電壓為ui的大小決定各比較器的輸出狀態,例如,當0≤ui<1時,c7~c1的輸出狀態都為0;當h≤vi<f時,比較器c6和c7的輸出co6=co7=1,其余各比較器的狀態均為0。

比較器的輸出狀態由d觸發器存儲,經優先編碼器編碼,得到數字量輸出。

圖9.2.4 3位并行a/d轉換器,設u1變化范圍是0~yrⅢ,輸出3位數字量為d2dido,3位并行比較型a/d轉換器的輸人、輸出關系如表9.2.1所示。

優先編碼器,逐次比較型a/d轉換器,轉換原理,直接a/d轉換器中,逐次比較型a/d轉換器是采用較多的一種。它的轉換過程與用天平稱物重相似。天平稱重過程是,從最重的砝碼開始試放,與被稱物體進行比較,若物體重于砝碼,則該砝碼保留,否則移去。再加上第二個次重法碼……照此進行,一直加到最小一個砝碼。將所有留下的砝碼重量相加,就得物體重量。仿照這一思路,逐次比較型a/d轉換器,就是將輸入模擬信號與不同的參考電壓做多次比較,使轉換所得的數字量在數值上逐次逼近輸人模擬量。

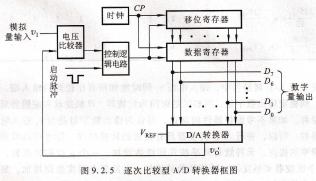

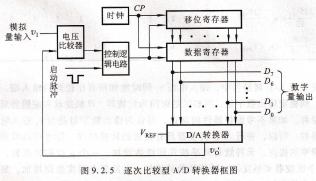

8位逐次比較型a/d轉換器框圖如圖9.2.5所示。它由控制邏輯電路、數據寄存器、移位寄存器、d/a轉換器及電壓比較器組成。

cp模擬量輸入uid1t數字,j量輸出較,如果vi≥ic廾,則比較器輸出為1,如果vi(t尹,則比較器輸出為0,此結果存于數據寄存器的d7位;第二個cp使移位寄存器為01000000。如果最高位已存1,則此時d/a轉換器的輸出電壓u=lv1再與l.f些相比較,如果vi≥ui,則次高位d6存1,否則d6=0;如果最高位為0,則u=ul蓄氣逐次比較型a/d轉換器框圖.

電路啟動后,第一個cp將移位寄存器置為10000000,該數字經數據寄存器送人d/a轉換器。輸人模擬電壓vi首先與10000000所對應的電壓相比,時鐘移位寄存器,數據寄存器,vefd/a轉換器,啟動脈沖數模與模數交換器.

hd63484p98別作為比較器c1~c7的參考電壓。輸入電壓為ui的大小決定各比較器的輸出狀態,例如,當0≤ui<1時,c7~c1的輸出狀態都為0;當h≤vi<f時,比較器c6和c7的輸出co6=co7=1,其余各比較器的狀態均為0。

比較器的輸出狀態由d觸發器存儲,經優先編碼器編碼,得到數字量輸出。

圖9.2.4 3位并行a/d轉換器,設u1變化范圍是0~yrⅢ,輸出3位數字量為d2dido,3位并行比較型a/d轉換器的輸人、輸出關系如表9.2.1所示。

優先編碼器,逐次比較型a/d轉換器,轉換原理,直接a/d轉換器中,逐次比較型a/d轉換器是采用較多的一種。它的轉換過程與用天平稱物重相似。天平稱重過程是,從最重的砝碼開始試放,與被稱物體進行比較,若物體重于砝碼,則該砝碼保留,否則移去。再加上第二個次重法碼……照此進行,一直加到最小一個砝碼。將所有留下的砝碼重量相加,就得物體重量。仿照這一思路,逐次比較型a/d轉換器,就是將輸入模擬信號與不同的參考電壓做多次比較,使轉換所得的數字量在數值上逐次逼近輸人模擬量。

8位逐次比較型a/d轉換器框圖如圖9.2.5所示。它由控制邏輯電路、數據寄存器、移位寄存器、d/a轉換器及電壓比較器組成。

cp模擬量輸入uid1t數字,j量輸出較,如果vi≥ic廾,則比較器輸出為1,如果vi(t尹,則比較器輸出為0,此結果存于數據寄存器的d7位;第二個cp使移位寄存器為01000000。如果最高位已存1,則此時d/a轉換器的輸出電壓u=lv1再與l.f些相比較,如果vi≥ui,則次高位d6存1,否則d6=0;如果最高位為0,則u=ul蓄氣逐次比較型a/d轉換器框圖.

電路啟動后,第一個cp將移位寄存器置為10000000,該數字經數據寄存器送人d/a轉換器。輸人模擬電壓vi首先與10000000所對應的電壓相比,時鐘移位寄存器,數據寄存器,vefd/a轉換器,啟動脈沖數模與模數交換器.

公網安備44030402000607

公網安備44030402000607